## 4 General-Purpose Input/Output (GPIO)

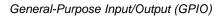

The GPIO multiplexing (MUX) registers are used to select the operation of shared pins. The pins are named by their general purpose I/O name (i.e., GPIO0 - GPIO38). These pins can be individually selected to operate as digital I/O, referred to as GPIO, or connected to one of up to three peripheral I/O signals (via the GPxMUXn registers). If selected for digital I/O mode, registers are provided to configure the pin direction (via the GPxDIR registers). You can also qualify the input signals to remove unwanted noise (via the GPxQSELn, GPACTRL, and GPBCTRL registers).

## 4.1 GPIO Module Overview

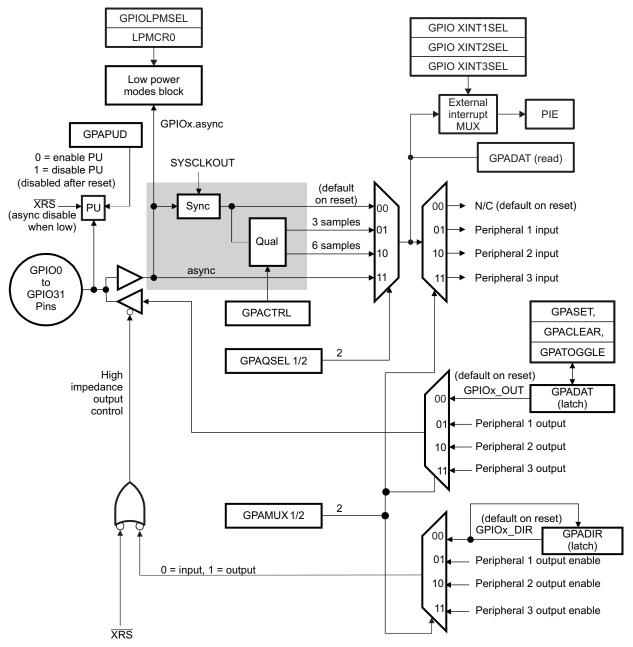

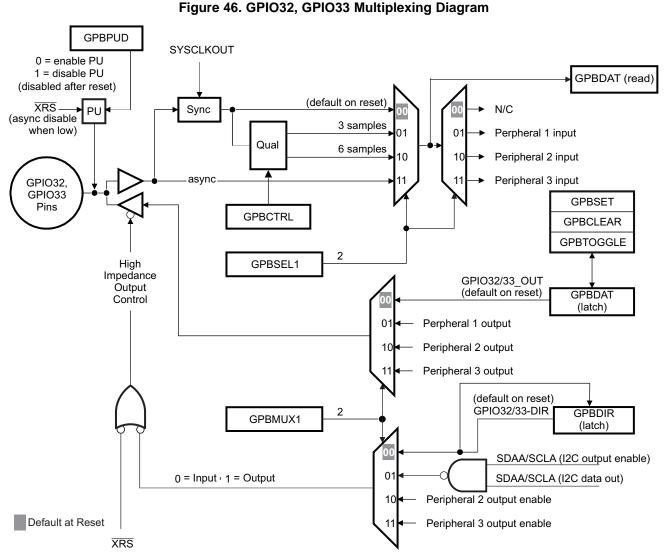

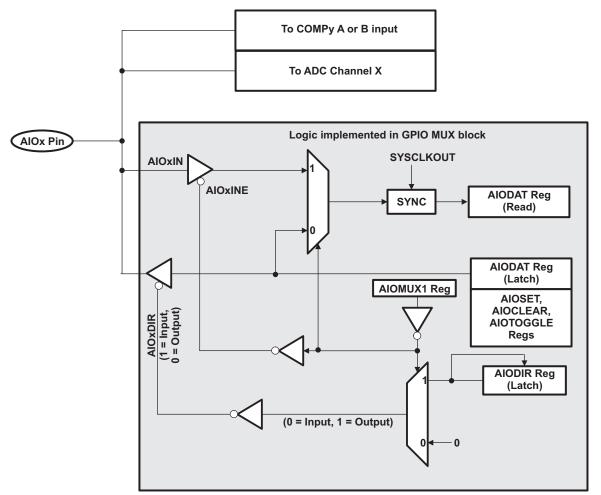

Up to three independent peripheral signals are multiplexed on a single GPIO-enabled pin in addition to individual pin bit-I/O capability. There are three I/O ports. Port A consists of GPIO0-GPIO31, port B consists of GPIO32-GPIO38. The analog port consists of AIO0-AIO15. Figure 45 shows the basic modes of operation for the GPIO module. Note that GPIO functionality is provided on JTAG pins as well.

General-Purpose Input/Output (GPIO)

Figure 45. GPIO0 to GPIO31 Multiplexing Diagram

A GPxDAT latch/read are accessed at the same memory location.

- A The GPIOINENCLK bit in the PCLKCR3 register does not affect the above GPIOs (I<sup>2</sup>C pins) since the pins are bi-directional.

- B The input qualification circuit is not reset when modes are changed (such as changing from output to input mode). Any state will get flushed by the circuit eventually.

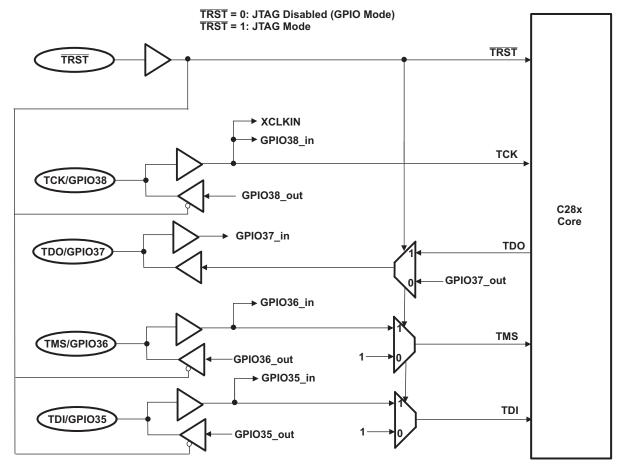

# 4.1.1 JTAG Port

On the 2802x device, the JTAG port is reduced to 5 pins (TRST, TCK, TDI, TMS, TDO). TCK, TDI, TMS and TDO pins are also GPIO pins. The TRST signal selects either JTAG or GPIO operating mode for the pins in Figure 47.

**NOTE:** In 2802x devices, the JTAG pins may also be used as GPIO pins. Care should be taken in the board design to ensure that the circuitry connected to these pins do not affect the emulation capabilities of the JTAG pin function. Any circuitry connected to these pins should not prevent the emulator from driving (or being driven by) the JTAG pins for successful debug.

# Figure 47. JTAG Port/GPIO Multiplexing

- A The ADC/Comparator path is always enabled, irrespective of the AIOMUX1 value.

- B The AIO section is blocked off when the corresponding AIOMUX1 bit is 1.

# 4.2 Configuration Overview

The pin function assignments, input qualification, and the external interrupt sources are all controlled by the GPIO configuration control registers. In addition, you can assign pins to wake the device from the HALT and STANDBY low power modes and enable/disable internal pullup resistors. Table 49 and Table 50 list the registers that are used to configure the GPIO pins to match the system requirements.

| Name (1) | Address | Size (x16) | Register Description                               | Bit Description |

|----------|---------|------------|----------------------------------------------------|-----------------|

| GPACTRL  | 0x6F80  | 2          | GPIO A Control Register (GPIO0-GPIO31)             | Figure 55       |

| GPAQSEL1 | 0x6F82  | 2          | GPIO A Qualifier Select 1 Register (GPIO0-GPIO15)  | Figure 57       |

| GPAQSEL2 | 0x6F84  | 2          | GPIO A Qualifier Select 2 Register (GPIO16-GPIO31) | Figure 58       |

| GPAMUX1  | 0x6F86  | 2          | GPIO A MUX 1 Register (GPIO0-GPIO15)               | Figure 51       |

| GPAMUX2  | 0x6F88  | 2          | GPIO A MUX 2 Register (GPIO16-GPIO31)              | Figure 52       |

| GPADIR   | 0x6F8A  | 2          | GPIO A Direction Register (GPIO0-GPIO31)           | Figure 60       |

| GPAPUD   | 0x6F8C  | 2          | GPIO A Pull Up Disable Register (GPIO0-GPIO31)     | Figure 63       |

| GPBCTRL  | 0x6F90  | 2          | GPIO B Control Register (GPIO32-GPIO38)            | Figure 56       |

| GPBQSEL1 | 0x6F92  | 2          | GPIO B Qualifier Select 1 Register (GPIO32-GPIO38) | Figure 59       |

| GPBMUX1  | 0x6F96  | 2          | GPIO B MUX 1 Register (GPIO32-GPIO38)              | Figure 53       |

| GPBDIR   | 0x6F9A  | 2          | GPIO B Direction Register (GPIO32-GPIO38)          | Figure 61       |

| GPBPUD   | 0x6F9C  | 2          | GPIO B Pull Up Disable Register (GPIO32-GPIO38)    | Figure 64       |

| AIOMUX1  | 0x6FB6  | 2          | Analog, I/O MUX 1 register (AIO0 - AIO15)          | Figure 54       |

| AIODIR   | 0x6FBA  | 2          | Analog, I/O Direction Register (AIO0 - AIO15)      | Figure 62       |

## Table 49. GPIO Control Registers

<sup>(1)</sup> The registers in this table are EALLOW protected. See Section 5.2 for more information.

# Table 50. GPIO Interrupt and Low Power Mode Select Registers

| Name <sup>(1)</sup> | Address | Size<br>(x16) | Register Description                             | Bit Description |

|---------------------|---------|---------------|--------------------------------------------------|-----------------|

| GPIOXINT1SEL        | 0x6FE0  | 1             | XINT1 Source Select Register (GPIO0-GPIO31)      | Figure 71       |

| GPIOXINT2SEL        | 0x6FE1  | 1             | XINT2 Source Select Register (GPIO0-GPIO31)      | Figure 71       |

| GPIOXINT3SEL        | 0x6FE2  | 1             | XINT3 Source Select Register (GPIO0 - GPIO31)    | Figure 71       |

| GPIOLPMSEL          | 0x6FE8  | 1             | LPM wakeup Source Select Register (GPIO0-GPIO31) | Figure 72       |

<sup>(1)</sup> The registers in this table are EALLOW protected. See Section 5.2 for more information.

To plan configuration of the GPIO module, consider the following steps:

### Step 1. Plan the device pin-out:

Through a pin multiplexing scheme, a lot of flexibility is provided for assigning functionality to the GPIO-capable pins. Before getting started, look at the peripheral options available for each pin, and plan pin-out for your specific system. Will the pin be used as a general purpose input or output (GPIO) or as one of up to three available peripheral functions? Knowing this information will help determine how to further configure the pin.

### Step 2. Enable or disable internal pull-up resistors:

To enable or disable the internal pullup resistors, write to the respective bits in the GPIO pullup disable (GPAPUD and GPBPUD) registers. For pins that can function as ePWM output pins, the internal pullup resistors are disabled by default. All other GPIO-capable pins have the pullup enabled by default. The AIOx pins do not have internal pull-up resistors.

### Step 3. Select input qualification:

If the pin will be used as an input, specify the required input qualification, if any. The input qualification is specified in the GPACTRL, GPBCTRL, GPAQSEL1, GPAQSEL2, GPBQSEL1, and GPBQSEL2 registers. By default, all of the input signals are synchronized to SYSCLKOUT only.

## Step 4. Select the pin function:

Configure the GPxMUXn or AIOMUXn registers such that the pin is a GPIO or one of three available peripheral functions. By default, all GPIO-capable pins are configured at reset as general purpose input pins.

## Step 5. For digital general purpose I/O, select the direction of the pin:

If the pin is configured as an GPIO, specify the direction of the pin as either input or output in the GPADIR, GPBDIR, or AIODIR registers. By default, all GPIO pins are inputs. To change the pin from input to output, first load the output latch with the value to be driven by writing the appropriate value to the GPxCLEAR, GPxSET, or GPxTOGGLE (or AIOCLEAR, AIOSET, or AIOTOGGLE) registers. Once the output latch is loaded, change the pin direction from input to output via the GPxDIR registers. The output latch for all pins is cleared at reset.

### Step 6. Select low power mode wake-up sources:

Specify which pins, if any, will be able to wake the device from HALT and STANDBY low power modes. The pins are specified in the GPIOLPMSEL register.

### Step 7. Select external interrupt sources:

Specify the source for the XINT1 - XINT3 interrupts. For each interrupt you can specify one of the port A signals as the source. This is done by specifying the source in the GPIOXINTnSEL register. The polarity of the interrupts can be configured in the XINTnCR register as described in Section 6.6.

**NOTE:** There is a 2-SYSCLKOUT cycle delay from when a write to configuration registers such as GPxMUXn and GPxQSELn occurs to when the action is valid

# 4.3 Digital General Purpose I/O Control

For pins that are configured as GPIO you can change the values on the pins by using the registers in Table 51.

| Name      | Address | Size (x16) | Register Description                        | Bit Description |

|-----------|---------|------------|---------------------------------------------|-----------------|

| GPADAT    | 0x6FC0  | 2          | GPIO A Data Register (GPIO0-GPIO31)         | Figure 65       |

| GPASET    | 0x6FC2  | 2          | GPIO A Set Register (GPIO0-GPIO31)          | Figure 68       |

| GPACLEAR  | 0x6FC4  | 2          | GPIO A Clear Register (GPIO0-GPIO31)        | Figure 68       |

| GPATOGGLE | 0x6FC6  | 2          | GPIO A Toggle Register (GPIO0-GPIO31)       | Figure 68       |

| GPBDAT    | 0x6FC8  | 2          | GPIO B Data Register (GPIO32-GPIO38)        | Figure 66       |

| GPBSET    | 0x6FCA  | 2          | GPIO B Set Register (GPIO32-GPIO38)         | Figure 69       |

| GPBCLEAR  | 0x6FCC  | 2          | GPIO B Clear Register (GPIO32-GPIO38)       | Figure 69       |

| GPBTOGGLE | 0x6FCE  | 2          | GPIO B Toggle Register (GPIO32-GPIO38)      | Figure 69       |

| AIODAT    | 0x6FD8  | 2          | Analog I/O Data Register (AIO0 - AIO15)     | Figure 67       |

| AIOSET    | 0x6FDA  | 2          | Analog I/O Data Set Register (AIO0 - AIO15) | Figure 70       |

| AIOCLEAR  | 0x6FDC  | 2          | Analog I/O Clear Register (AIO0 - AIO15)    | Figure 70       |

| AIOTOGGLE | 0x6FDE  | 2          | Analog I/O Toggle Register (AIO0 - AIO15)   | Figure 70       |

### Table 51. GPIO Data Registers

## GPxDAT/AIODAT Registers

Each I/O port has one data register. Each bit in the data register corresponds to one GPIO pin. No matter how the pin is configured (GPIO or peripheral function), the corresponding bit in the data register reflects the current state of the pin after qualification (This does not apply to AIOx pins). Writing to the GPxDAT/AIODAT register clears or sets the corresponding output latch and if the pin is enabled as a general purpose output (GPIO output) the pin will also be driven either low or high. If the pin is not configured as a GPIO output then the value will be latched, but the pin will not be driven. Only if the pin is later configured as a GPIO output, will the latched value be driven onto the pin.

When using the GPxDAT register to change the level of an output pin, you should be cautious not to accidentally change the level of another pin. For example, if you mean to change the output latch level of GPIOA1 by writing to the GPADAT register bit 0 using a read-modify-write instruction, a problem can occur if another I/O port A signal changes level between the read and the write stage of the instruction. Following is an analysis of why this happens:

The GPxDAT registers reflect the state of the pin, not the latch. This means the register reflects the actual pin value. However, there is a lag between when the register is written to when the new pin value is reflected back in the register. This may pose a problem when this register is used in subsequent program statements to alter the state of GPIO pins. An example is shown below where two program statements attempt to drive two different GPIO pins that are currently low to a high state.

If Read-Modify-Write operations are used on the GPxDAT registers, because of the delay between the output and the input of the first instruction (I1), the second instruction (I2) will read the old value and write it back.

GpioDataRegs.GPADAT.bit.GPIO1 = 1 ; Il performs read-modify-write of GPADAT GpioDataRegs.GPADAT.bit.GPIO2 = 1 ; I2 also a read-modify-write of GPADAT. ; It gets the old value of GPIO1 due to the delay

The second instruction will wait for the first to finish its write due to the write-followed-by-read protection on this peripheral frame. There will be some lag, however, between the write of (I1) and the GPxDAT bit reflecting the new value (1) on the pin. During this lag, the second instruction will read the old value of GPIO1 (0) and write it back along with the new value of GPIO2 (1). Therefore, GPIO1 pin stays low.

One solution is to put some NOP's between instructions. A better solution is to use the GPxSET/GPxCLEAR/GPxTOGGLE registers instead of the GPxDAT registers. These registers always read back a 0 and writes of 0 have no effect. Only bits that need to be changed can be specified

without disturbing any other bit(s) that are currently in the process of changing.

## GPxSET/AIOSET Registers

The set registers are used to drive specified GPIO pins high without disturbing other pins. Each I/O port has one set register and each bit corresponds to one GPIO pin. The set registers always read back 0. If the corresponding pin is configured as an output, then writing a 1 to that bit in the set register will set the output latch high and the corresponding pin will be driven high. If the pin is not configured as a GPIO output, then the value will be latched but the pin will not be driven. Only if the pin is later configured as a GPIO output will the latched value will be driven onto the pin. Writing a 0 to any bit in the set registers has no effect.

## GPxCLEAR/AIOCLEAR Registers

The clear registers are used to drive specified GPIO pins low without disturbing other pins. Each I/O port has one clear register. The clear registers always read back 0. If the corresponding pin is configured as a general purpose output, then writing a 1 to the corresponding bit in the clear register will clear the output latch and the pin will be driven low. If the pin is not configured as a GPIO output, then the value will be latched but the pin will not be driven. Only if the pin is later configured as a GPIO output will the latched value will be driven onto the pin. Writing a 0 to any bit in the clear registers has no effect.

## GPxTOGGLE/AIOTOGGLE Registers

The toggle registers are used to drive specified GPIO pins to the opposite level without disturbing other pins. Each I/O port has one toggle register. The toggle registers always read back 0. If the corresponding pin is configured as an output, then writing a 1 to that bit in the toggle register flips the output latch and pulls the corresponding pin in the opposite direction. That is, if the output pin is driven low, then writing a 1 to the corresponding bit in the toggle register will pull the pin high. Likewise, if the output pin is high, then writing a 1 to the corresponding bit in the toggle register will pull the pin high. Likewise, if the output pin is not configured as a GPIO output, then the value will be latched but the pin will not be driven. Only if the pin is later configured as a GPIO output will the latched value will be driven onto the pin. Writing a 0 to any bit in the toggle registers has no effect.

## 4.4 Input Qualification

The input qualification scheme has been designed to be very flexible. You can select the type of input qualification for each GPIO pin by configuring the GPAQSEL1, GPAQSEL2, GPBQSEL1 and GPBQSEL2 registers. In the case of a GPIO input pin, the qualification can be specified as only synchronize to SYSCLKOUT or qualification by a sampling window. For pins that are configured as peripheral inputs, the input can also be asynchronous in addition to synchronized to SYSCLKOUT or qualified by a sampling window. The remainder of this section describes the options available.

## 4.4.1 No Synchronization (asynchronous input)

This mode is used for peripherals where input synchronization is not required or the peripheral itself performs the synchronization. Examples include communication ports SCI, SPI, and I<sup>2</sup>C. In addition, it may be desirable to have the ePWM trip zone ( $\overline{TZn}$ ) signals function independent of the presence of SYSCLKOUT.

The asynchronous option is not valid if the pin is used as a general purpose digital input pin (GPIO). If the pin is configured as a GPIO input and the asynchronous option is selected then the qualification defaults to synchronization to SYSCLKOUT as described in Section 4.4.2.

# 4.4.2 Synchronization to SYSCLKOUT Only

This is the default qualification mode of all the pins at reset. In this mode, the input signal is only synchronized to the system clock (SYSCLKOUT). Because the incoming signal is asynchronous, it can take up to a SYSCLKOUT period of delay in order for the input to the DSP to be changed. No further qualification is performed on the signal.

#### 4.4.3 Qualification Using a Sampling Window

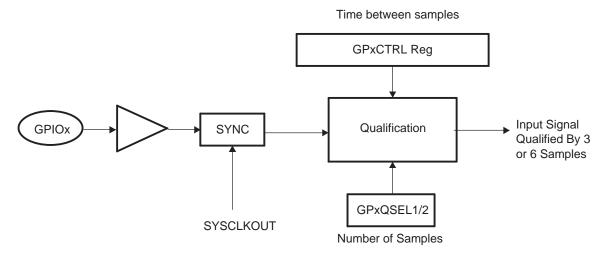

In this mode, the signal is first synchronized to the system clock (SYSCLKOUT) and then qualified by a specified number of cycles before the input is allowed to change. Figure 49 and Figure 50 show how the input qualification is performed to eliminate unwanted noise. Two parameters are specified by the user for this type of qualification: 1) the sampling period, or how often the signal is sampled, and 2) the number of samples to be taken.

### Figure 49. Input Qualification Using a Sampling Window

### Time between samples (sampling period):

To qualify the signal, the input signal is sampled at a regular period. The sampling period is specified by the user and determines the time duration between samples, or how often the signal will be sampled, relative to the CPU clock (SYSCLKOUT).

The sampling period is specified by the qualification period (QUALPRDn) bits in the GPxCTRL register. The sampling period is configurable in groups of 8 input signals. For example, GPIO0 to GPIO7 use GPACTRL[QUALPRD0] setting and GPIO8 to GPIO15 use GPACTRL[QUALPRD1]. Table 52 and Table 53 show the relationship between the sampling period or sampling frequency and the GPxCTRL[QUALPRDn] setting.

www.ti.com

## Table 52. Sampling Period

#### Sampling Period

| If GPxCTRL[QUALPRDn] = 0 | 1 × T <sub>SYSCLKOUT</sub>                                      |

|--------------------------|-----------------------------------------------------------------|

| If GPxCTRL[QUALPRDn] ≠ 0 | 2 × GPxCTRL[QUALPRDn] × T <sub>SYSCLKOUT</sub>                  |

|                          | Where T <sub>SYSCLKOUT</sub> is the period in time of SYSCLKOUT |

#### Table 53. Sampling Frequency

#### Sampling Frequency

| If GPxCTRL[QUALPRDn] = 0 | f <sub>sysclkout</sub>                                     |

|--------------------------|------------------------------------------------------------|

| If GPxCTRL[QUALPRDn] ≠ 0 | f <sub>SYSCLKOUT</sub> × 1 ÷ (2 × GPxCTRL[QUALPRDn])       |

|                          | Where f <sub>SYSCLKOUT</sub> is the frequency of SYSCLKOUT |

From these equations, the minimum and maximum time between samples can be calculated for a given SYSCLKOUT frequency:

#### **Example: Maximum Sampling Frequency:**

If GPxCTRL[QUALPRDn] = 0 then the sampling frequency is f<sub>SYSCLKOUT</sub> If, for example,  $f_{SYSCLKOUT} = 60 \text{ MHz}$ then the signal will be sampled at 60 MHz or one sample every 16.67 ns.

#### **Example: Minimum Sampling Frequency:**

```

If GPxCTRL[QUALPRDn] = 0xFF (i.e. 255)

then the sampling frequency is f<sub>SYSCLKOUT</sub> × 1 ÷ (2 × GPxCTRL[QUALPRDn])

If, for example, f<sub>SYSCLKOUT</sub> = 60 MHz

then the signal will be sampled at 60 MHz x 1 \div (2 x 255) or one sample every 8.5 \mus.

```

#### Number of samples:

The number of times the signal is sampled is either 3 samples or 6 samples as specified in the qualification selection (GPAQSEL1, GPAQSEL2, GPBQSEL1, and GPBQSEL2) registers. When 3 or 6 consecutive cycles are the same, then the input change will be passed through to the DSP.

### **Total Sampling Window Width:**

The sampling window is the time during which the input signal will be sampled as shown in Figure 50. By using the equation for the sampling period along with the number of samples to be taken, the total width of the window can be determined.

For the input qualifier to detect a change in the input, the level of the signal must be stable for the duration of the sampling window width or longer.

The number of sampling periods within the window is always one less then the number of samples taken. For a thee-sample window, the sampling window width is 2 sampling periods wide where the sampling period is defined in Table 52. Likewise, for a six-sample window, the sampling window width is 5 sampling periods wide. Table 54 and Table 55 show the calculations that can be used to determine the total sampling window width based on GPxCTRL[QUALPRDn] and the number of samples taken.

#### Table 54. Case 1: Three-Sample Sampling Window Width

|                          | Total Sampling Window Width                                     |

|--------------------------|-----------------------------------------------------------------|

| If GPxCTRL[QUALPRDn] = 0 | 2 × T <sub>SYSCLKOUT</sub>                                      |

| If GPxCTRL[QUALPRDn] ≠ 0 | 2 × 2 × GPxCTRL[QUALPRDn] × T <sub>SYSCLKOUT</sub>              |

|                          | Where T <sub>SYSCLKOUT</sub> is the period in time of SYSCLKOUT |

## Table 55. Case 2: Six-Sample Sampling Window Width

|                          | Total Sampling Window Width                                     |

|--------------------------|-----------------------------------------------------------------|

| If GPxCTRL[QUALPRDn] = 0 | 5 × T <sub>SYSCLKOUT</sub>                                      |

| If GPxCTRL[QUALPRDn] ≠ 0 | 5 × 2 × GPxCTRL[QUALPRDn] × T <sub>SYSCLKOUT</sub>              |

|                          | Where T <sub>SYSCLKOUT</sub> is the period in time of SYSCLKOUT |

|                          |                                                                 |

**NOTE:** The external signal change is asynchronous with respect to both the sampling period and SYSCLKOUT. Due to the asynchronous nature of the external signal, the input should be held stable for a time greater than the sampling window width to make sure the logic detects a change in the signal. The extra time required can be up to an additional sampling period +  $T_{SYSCLKOUT}$ .

The required duration for an input signal to be stable for the qualification logic to detect a change is described in the device specific data manual.

### **Example Qualification Window:**

For the example shown in Figure 50, the input qualification has been configured as follows:

- GPxQSEL1/2 = 1,0. This indicates a six-sample qualification.

- GPxCTRL[QUALPRDn] = 1. The sampling period is  $t_w(SP) = 2 \times GPxCTRL[QUALPRDn] \times T_{SYSCLKOUT}$ .

This configuration results in the following:

- The width of the sampling window is: .

t<sub>w</sub>(IQSW) = 5 × t<sub>w</sub>(SP) = 5 × 2 × GPxCTRL[QUALPRDn] × T<sub>SYSCLKOUT</sub> or 5 × 2 × T<sub>SYSCLKOUT</sub>

- If, for example,  $T_{SYSCLKOUT} = 16.67$  ns, then the duration of the sampling window is:  $t_w(IQSW) = 5 \times 2 \times 16.67$  ns =166.7 ns.

- To account for the asynchronous nature of the input relative to the sampling period and SYSCLKOUT, up to an additional sampling period, t<sub>w</sub>(SP), + T<sub>SYSCLKOUT</sub> may be required to detect a change in the input signal. For this example:

$t_w(SP) + T_{SYSCLKOUT} = 333.4 \text{ ns} + 166.67 \text{ ns} = 500.1 \text{ ns}$

• In Figure 50, the glitch (A) is shorter then the qualification window and will be ignored by the input qualifier.

## Figure 50. Input Qualifier Clock Cycles

- A. This glitch will be ignored by the input qualifier. The QUALPRD bit field specifies the qualification sampling period. It can vary from 00 to 0xFF. If QUALPRD = 00, then the sampling period is 1 SYSCLKOUT cycle. For any other value "n", the qualification sampling period in 2n SYSCLKOUT cycles (i.e., at every 2n SYSCLKOUT cycles, the GPIO pin will be sampled).

- B. The qualification period selected via the GPxCTRL register applies to groups of 8 GPIO pins.

- C. The qualification block can take either three or six samples. The GPxQSELn Register selects which sample mode is used.

- D. In the example shown, for the qualifier to detect the change, the input should be stable for 10 SYSCLKOUT cycles or greater. In other words, the inputs should be stable for (5 x QUALPRD x 2) SYSCLKOUT cycles. That would ensure 5 sampling periods for detection to occur. Since external signals are driven asynchronously, an 13-SYSCLKOUT-wide pulse ensures reliable recognition.

General-Purpose Input/Output (GPIO)

## 4.5 GPIO and Peripheral Multiplexing (MUX)

Up to three different peripheral functions are multiplexed along with a general input/output (GPIO) function per pin. This allows you to pick and choose a peripheral mix that will work best for the particular application.

Table 57 and Table 58 show an overview of the possible multiplexing combinations sorted by GPIO pin. The second column indicates the I/O name of the pin on the device. Since the I/O name is unique, it is the best way to identify a particular pin. Therefore, the register descriptions in this section only refer to the GPIO name of a particular pin. The MUX register and particular bits that control the selection for each pin are indicated in the first column.

For example, the multiplexing for the GPIO6 pin is controlled by writing to GPAMUX[13:12]. By writing to these bits, the pin is configured as either GPIO6, or one of up to three peripheral functions. The GPIO6 pin can be configured as follows:

| GPAMUX1[13:12] Bit Setting | Pin Functionality Selected      |

|----------------------------|---------------------------------|

| If GPAMUX1[13:12] = 0,0    | Pin configured as GPIO6         |

| If GPAMUX1[13:12] = 0,1    | Pin configured as EPWM4A (O)    |

| If GPAMUX1[13:12] = 1,0    | Pin configured as EPWMSYNCI (I) |

| If GPAMUX1[13:12] = 1,1    | Pin configured as EPWMSYNCO (O) |

The 2802x and 2803x devices have different multiplexing schemes. If a peripheral is not available on a particular device, that MUX selection is reserved on that device and should not be used.

**NOTE:** If you should select a reserved GPIO MUX configuration that is not mapped to a peripheral, the state of the pin will be undefined and the pin may be driven. Reserved configurations are for future expansion and should not be selected. In the device MUX tables (Table 57 and Table 58) these options are indicated as Reserved.

Some peripherals can be assigned to more than one pin via the MUX registers. For example, in the 2803x device, the SPISIMOB can be assigned to either the GPIO12 or GPIO24 pin, depending on individual system requirements as shown below:

| Pin Assigned to SPISIMOB |        |  |  |  |  |

|--------------------------|--------|--|--|--|--|

| Choice 1                 | GPIO12 |  |  |  |  |

| or Choice 2              | GPIO24 |  |  |  |  |

**MUX Configuration** GPAMUX[25:24] = 1,1 GPAMUX2[17:16] = 1,1

If no pin is configured as an input to a peripheral, or if more than one pin is configured as an input for the same peripheral, then the input to the peripheral will either default to a 0 or a 1 as shown in Table 56. For example, if SPISIMOB were assigned to both GPIO12 and GPIO24, the input to the SPI peripheral would default to a high state as shown in Table 56 and the input would not be connected to GPIO12 or GPIO24.

Texas

RUMENTS

#### General-Purpose Input/Output (GPIO)

| Peripheral Input  | Description                | Default Input <sup>(1)</sup> |

|-------------------|----------------------------|------------------------------|

| TZ1-TZ3           | Trip zone 1-3              | 1                            |

| EPWMSYNCI         | ePWM Synch Input           | 0                            |

| ECAP1             | eCAP1 input                | 1                            |

| SPICLKA           | SPI-A clock                | 1                            |

| SPISTEA           | SPI-A transmit enable      | 0                            |

| SPISIMOA          | SPI-A Slave-in, master-out | 1                            |

| SPISOMIA          | SPI-A Slave-out, master-in | 1                            |

| SCIRXDA - SCIRXDB | SCI-A - SCI-B receive      | 1                            |

| SDAA              | l <sup>2</sup> C data      | 1                            |

| SCLA1             | l <sup>2</sup> C clock     | 1                            |

Table 56. Default State of Peripheral Input

<sup>(1)</sup> This value will be assigned to the peripheral input if more then one pin has been assigned to the peripheral function in the GPxMUX1/2 registers or if no pin has been assigned.

General-Purpose Input/Output (GPIO)

|                                                                                                           | Tal                 | ole 57. 2802x GPIO  | A MUX                   |                         |  |

|-----------------------------------------------------------------------------------------------------------|---------------------|---------------------|-------------------------|-------------------------|--|

| Default at Reset<br>Primary I/O Function Peripheral Selection Peripheral Selection 2 Peripheral Selection |                     |                     |                         |                         |  |

| GPAMUX1 Register<br>Bits                                                                                  | (GPAMUX1 bits = 00) | (GPAMUX1 bits = 01) | (GPAMUX1 bits = 10)     | (GPAMUX1 bits = 11      |  |

| 1-0                                                                                                       | GPIO0               | EPWM1A (O)          | Reserved <sup>(1)</sup> | Reserved <sup>(1)</sup> |  |

| 3-2                                                                                                       | GPIO1               | EPWM1B (O)          | Reserved                | COMP1OUT (O)            |  |

| 5-4                                                                                                       | GPIO2               | EPWM2A (O)          | Reserved                | Reserved <sup>(1)</sup> |  |

| 7-6                                                                                                       | GPIO3               | EPWM2B (O)          | Reserved                | COMP2OUT (O)            |  |

| 9-8                                                                                                       | GPIO4               | EPWM3A (O)          | Reserved                | Reserved <sup>(1)</sup> |  |

| 11-10                                                                                                     | GPIO5               | EPWM3B (O)          | Reserved                | ECAP1 (I/O)             |  |

| 13-12                                                                                                     | GPIO6               | EPWM4A (O)          | EPWMSYNCI (I)           | EPWMSYNCO (O)           |  |

| 15-14                                                                                                     | GPIO7               | EPWM4B (O)          | SCIRXDA (I)             | Reserved                |  |

| 17-16                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 19-18                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 21-20                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 23-22                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 25-24                                                                                                     | GPIO12              | TZ1 (I)             | SCITXDA (O)             | Reserved                |  |

| 27-26                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 29-28                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 31-30                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| GPAMUX2 Register<br>Bits                                                                                  | (GPAMUX2 bits = 00) | (GPAMUX2 bits = 01) | (GPAMUX2 bits = 10)     | (GPAMUX2 bits = 11      |  |

| 1-0                                                                                                       | GPIO16              | SPISIMOA (I/O)      | Reserved                | TZ2 (I)                 |  |

| 3-2                                                                                                       | GPIO17              | SPISOMIA (I/O)      | Reserved                | TZ3 (I)                 |  |

| 5-4                                                                                                       | GPIO18              | SPICLKA (I/O)       | SCITXDA (O)             | XCLKOUT (O)             |  |

| 7-6                                                                                                       | GPIO19/XCLKIN       | SPISTEA (I/O)       | SCIRXDA (I)             | ECAP1 (I/O)             |  |

| 9-8                                                                                                       | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 11-10                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 13-12                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 15-14                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 17-16                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 19-18                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 21-20                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 23-22                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 25-24                                                                                                     | GPIO28              | SCIRXDA (I)         | SDAA (I/OC)             | TZ2 (O)                 |  |

| 27-26                                                                                                     | GPIO29              | SCITXDA (O)         | SCLA (I/OC)             | TZ3 (O)                 |  |

| 29-28                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

| 31-30                                                                                                     | Reserved            | Reserved            | Reserved                | Reserved                |  |

<sup>(1)</sup> The word Reserved means that there is no peripheral assigned to this GPxMUX1/2 register setting. Should it be selected, the state of the pin will be undefined and the pin may be driven. This selection is a reserved configuration for future expansion.

## General-Purpose Input/Output (GPIO)

|                          | Default at Reset<br>Primary I/O Function | Peripheral Selection 1 | Peripheral Selection 2 | Peripheral Selection 3 |

|--------------------------|------------------------------------------|------------------------|------------------------|------------------------|

| GPBMUX1 Register<br>Bits | (GPBMUX1 bits = 00)                      | (GPBMUX1 bits = 01)    | (GPBMUX1 bits = 10)    | (GPBMUX1 bits = 11)    |

| 1,0                      | GPIO32                                   | SDAA (I/OC)            | EPWMSYNCI (I)          | ADCSOCAO (O)           |

| 3,2                      | GPIO33                                   | SCLA (I/OC)            | EPWMSYNCO (O)          | ADCSOCBO (O)           |

| 5,4                      | GPIO34                                   | COMP2OUT (O)           | Reserved               | Reserved               |

| 7,6                      | GPIO35 (TDI)                             | Reserved               | Reserved               | Reserved               |

| 9,8                      | GPIO36 (TMS)                             | Reserved               | Reserved               | Reserved               |

| 11,10                    | GPIO37 (TDO)                             | Reserved               | Reserved               | Reserved               |

| 13,12                    | GPIO38/XCLKIN (TCK)                      | Reserved               | Reserved               | Reserved               |

| 15,14                    | Reserved                                 | Reserved               | Reserved               | Reserved               |

| 17,16                    | Reserved                                 | Reserved               | Reserved               | Reserved               |

| 19,18                    | Reserved                                 | Reserved               | Reserved               | Reserved               |

| 21,20                    | Reserved                                 | Reserved               | Reserved               | Reserved               |

| 23,22                    | Reserved                                 | Reserved               | Reserved               | Reserved               |

| 25,24                    | Reserved                                 | Reserved               | Reserved               | Reserved               |

| 27,26                    | Reserved                                 | Reserved               | Reserved               | Reserved               |

| 29,28                    | Reserved                                 | Reserved               | Reserved               | Reserved               |

| 31,30                    | Reserved                                 | Reserved               | Reserved               | Reserved               |

## Table 58. 2802x GPIOB MUX

# Table 59. Analog MUX

|                       |                                | Default at Reset                                     |

|-----------------------|--------------------------------|------------------------------------------------------|

|                       | AIOx and Peripheral Selection1 | Peripheral Selection 2 and Peripheral<br>Selection 3 |

| AIOMUX1 Register bits | AIOMUX1 bits = 0,x             | AIOMUX1 bits = 1,x                                   |

| 1-0                   | ADCINA0 (I)                    | ADCINA0 (I)                                          |

| 3-2                   | ADCINA1 (I)                    | ADCINA1 (I)                                          |

| 5-4                   | AIO2 (I/O)                     | ADCINA2 (I), COMP1A (I)                              |

| 7-6                   | ADCINA3 (I)                    | ADCINA3 (I)                                          |

| 9-8                   | AIO4 (I/O)                     | ADCINA4 (I), COMP2A (I)                              |

| 11-10                 | ADCINA5 (I)                    | ADCINA5 (I)                                          |

| 13-12                 | AIO6 (I/O)                     | ADCINA6 (I)                                          |

| 15-14                 | ADCINA7 (I)                    | ADCINA7 (I)                                          |

| 17-16                 | ADCINB0 (I)                    | ADCINB0 (I)                                          |

| 19-18                 | ADCINB1 (I)                    | ADCINB1 (I)                                          |

| 21-20                 | AIO10 (I/O)                    | ADCINB2 (I), COMP1B (I)                              |

| 23-22                 | ADCINB3 (I)                    | ADCINB3 (I)                                          |

| 25-24                 | AIO12 (I/O)                    | ADCINB4 (I), COMP2B (I)                              |

| 27-26                 | ADCINB5 (I)                    | ADCINB5 (I)                                          |

| 29-28                 | AIO14 (I/O)                    | ADCINB6 (I)                                          |

| 31-30                 | ADCINB7 (I)                    | ADCINB7 (I)                                          |

## 4.6 Register Bit Definitions

|                   |                   |      |       | ГЦ    | jure 51           | . GFIU | FOILF           |       | I (GFA | WUAT) | Regis | lei |     |   |    |

|-------------------|-------------------|------|-------|-------|-------------------|--------|-----------------|-------|--------|-------|-------|-----|-----|---|----|

| 31                |                   |      |       |       | 26                | 25     | 24              | 23    |        |       |       |     |     |   | 16 |

|                   |                   | Rese | erved |       |                   | GPI    | GPIO12 Reserved |       |        |       |       |     |     |   |    |

| R-0               |                   |      |       |       |                   | R/V    | V-0             | R-0   |        |       |       |     |     |   |    |

| 15                | 14                | 13   | 12    | 11    | 10                | 9      | 8               | 7     | 6      | 5     | 4     | 3   | 2   | 1 | 0  |

| GP                | GPIO7 GPIO6 GPIO5 |      | 105   | GPIO4 |                   | GPIO3  |                 | GPIO2 |        | GPIO1 |       | GP  | IO0 |   |    |

| R/W-0 R/W-0 R/W-0 |                   | V-0  | R/V   | V-0   | R/W-0 R/W-0 R/W-0 |        |                 |       |        | R/\   | V-0   |     |     |   |    |

|                   |                   |      |       |       |                   |        |                 |       |        |       |       |     |     |   |    |

## Figure 51. GPIO Port A MUX 1 (GPAMUX1) Register

LEGEND- R/W = Read/Write; R = Read only; -n = value after reset

## Table 60. GPIO Port A Multiplexing 1 (GPAMUX1) Register Field Descriptions

| Bits  | Field    | Value | Description <sup>(1)</sup>                      |

|-------|----------|-------|-------------------------------------------------|

| 31-26 | Reserved |       | Reserved                                        |

| 25-24 | GPIO12   |       | Configure the GPIO12 pin as:                    |

|       |          | 00    | GPIO12 - General purpose I/O 12 (default) (I/O) |

|       |          | 01    | TZ1 - Trip zone 1 (I)                           |

|       |          | 10    | SCITXDA - SCI-A Transmit (O)                    |

|       |          | 11    | Reserved                                        |

| 23-16 | Reserved |       |                                                 |

| 15-14 | GPIO7    |       | Configure the GPIO7 pin as:                     |

|       |          | 00    | GPIO7 - General purpose I/O 7 (default) (I/O)   |

|       |          | 01    | EPWM4B - ePWM4 output B (O)                     |

|       |          | 10    | SCIRXDA (I) - SCI-A Receive (I)                 |

|       |          | 11    | Reserved                                        |

| 13-12 | GPIO6    |       | Configure the GPIO6 pin as:                     |

|       |          | 00    | GPIO6 - General purpose I/O 6 (default)         |

|       |          | 01    | EPWM4A - ePWM4 output A (O)                     |

|       |          | 10    | EPWMSYNCI - ePWM Synch-in (I)                   |

|       |          | 11    | EPWMSYNCO - ePWM Synch-out (O)                  |

| 11-10 | GPIO5    |       | Configure the GPIO5 pin as:                     |

|       |          | 00    | GPIO5 - General purpose I/O 5 (default) (I/O)   |

|       |          | 01    | EPWM3B - ePWM3 output B                         |

|       |          | 10    | Reserved                                        |

|       |          | 11    | ECAP1 - eCAP1 (I/O)                             |

| 9-8   | GPIO4    |       | Configure the GPIO4 pin as:                     |

|       |          | 00    | GPIO4 - General purpose I/O 4 (default) (I/O)   |

|       |          | 01    | EPWM3A - ePWM3 output A (O)                     |

|       |          | 10    | Reserved. <sup>(2)</sup>                        |

|       |          | 11    | Reserved. <sup>(2)</sup>                        |

| 7-6   | GPIO3    |       | Configure the GPIO3 pin as:                     |

|       |          | 00    | GPIO3 - General purpose I/O 3 (default) (I/O)   |

|       |          | 01    | EPWM2B - ePWM2 output B (O)                     |

|       |          | 10    | Reserved                                        |

|       |          | 11    | COMP2OUT (O)                                    |

<sup>(1)</sup> This register is EALLOW protected. See Section 5.2 for more information.

<sup>(2)</sup> If reserved configurations are selected, then the state of the pin will be undefined and the pin may be driven. These selections are reserved for future expansion and should not be used.

### Table 60. GPIO Port A Multiplexing 1 (GPAMUX1) Register Field Descriptions (continued)

| Bits | Field | Value | Description <sup>(1)</sup>                        |

|------|-------|-------|---------------------------------------------------|

| 5-4  | GPIO2 |       | Configure the GPIO2 pin as:                       |

|      |       | 00    | GPIO2 (I/O) General purpose I/O 2 (default) (I/O) |

|      |       | 01    | EPWM2A - ePWM2 output A (O)                       |

|      |       | 10    | Reserved. <sup>(2)</sup>                          |

|      |       | 11    | Reserved. <sup>(2)</sup>                          |

| 3-2  | GPIO1 |       | Configure the GPIO1 pin as:                       |

|      |       | 00    | GPIO1 - General purpose I/O 1 (default) (I/O)     |

|      |       | 01    | EPWM1B - ePWM1 output B (O)                       |

|      |       | 10    | Reserved                                          |

|      |       | 11    | COMP1OUT (O) - Comparator 1 output                |

| 1-0  | GPIO0 |       | Configure the GPIO0 pin as:                       |

|      |       | 00    | GPIO0 - General purpose I/O 0 (default) (I/O)     |

|      |       | 01    | EPWM1A - ePWM1 output A (O)                       |

|      |       | 10    | Reserved. <sup>(2)</sup>                          |

|      |       | 11    | Reserved. <sup>(2)</sup>                          |

## Figure 52. GPIO Port A MUX 2 (GPAMUX2) Register

| 31    | 28                      | 27  | 26  | 25          | 24   | 23                              |                   |   |       |        |          |   | 16 |  |       |  |  |  |

|-------|-------------------------|-----|-----|-------------|------|---------------------------------|-------------------|---|-------|--------|----------|---|----|--|-------|--|--|--|

| Rese  | erved                   | GPI | O29 | GPI         | D128 |                                 | Rese              |   |       |        | Reserved |   |    |  | erved |  |  |  |

| R/W-0 | R/W-0 R/W-0 R/W-0 R/W-0 |     | V-0 | R/W-0 R/W-0 |      |                                 | R/W-0             |   | R/W-0 |        |          |   |    |  |       |  |  |  |

| 15    |                         |     |     |             | 8    | 7                               | 6                 | 5 | 4     | 3      | 2        | 1 | 0  |  |       |  |  |  |

|       | Reserved                |     |     |             |      | GPIO19 GPIO18 GPIO <sup>2</sup> |                   |   | O17   | GPIO16 |          |   |    |  |       |  |  |  |

|       | R-0                     |     |     |             |      |                                 | R/W-0 R/W-0 R/W-0 |   |       | V-0    | R/W-0    |   |    |  |       |  |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 61. GPIO Port A MUX 2 (GPAMUX2) Register Field Descriptions

| Bits  | Field         | Value | Description <sup>(1)</sup>                          |

|-------|---------------|-------|-----------------------------------------------------|

| 31-28 | Reserved      |       | Reserved                                            |

| 27-26 | GPIO29        |       | Configure the GPIO29 pin as:                        |

|       |               | 00    | GPIO29 (I/O) General purpose I/O 29 (default) (I/O) |

|       |               | 01    | SCITXDA - SCI-A transmit. (O)                       |

|       |               | 10    | SCLA (I/OC)                                         |

|       |               | 11    | TZ3 - Trip zone 3(I)                                |

| 25-24 | GPIO28        |       | Configure the GPIO28 pin as:                        |

|       |               | 00    | GPIO28 (I/O) General purpose I/O 28 (default) (I/O) |

|       |               | 01    | SCIRXDA - SCI-A receive (I)                         |

|       |               | 10    | SDAA (I/OC)                                         |

|       |               | 11    | TZ2 - Trip zone 2(I)                                |

| 23-8  | Reserved      | 11    | Reserved                                            |

| 7-6   | GPIO19/XCLKIN |       | Configure the GPIO19 pin as:                        |

|       |               | 00    | GPIO19 - General purpose I/O 19 (default) (I/O)     |

|       |               | 01    | SPISTEA - SPI-A slave transmit enable (I/O)         |

|       |               | 10    | SCIRXDA (I)                                         |

|       |               | 11    | ECAP1 (I/O)                                         |

<sup>(1)</sup> This register is EALLOW protected. See Section 5.2 for more information.

## Table 61. GPIO Port A MUX 2 (GPAMUX2) Register Field Descriptions (continued)

| Bits | Field  | Value | Description <sup>(1)</sup>                      |

|------|--------|-------|-------------------------------------------------|

| 5-4  | GPIO18 |       | Configure the GPIO18 pin as:                    |

|      |        | 00    | GPIO18 - General purpose I/O 18 (default) (I/O) |

|      |        | 01    | SPICLKA - SPI-A clock (I/O)                     |

|      |        | 10    | SCITXDA (O)                                     |

|      |        | 11    | XCLKOUT (O) - External clock output             |

| 3-2  | GPIO17 |       | Configure the GPIO17 pin as:                    |

|      |        | 00    | GPIO17 - General purpose I/O 17 (default) (I/O) |

|      |        | 01    | SPISOMIA - SPI-A slave-out, master-in (I/O)     |

|      |        | 10    | Reserved                                        |

|      |        | 11    | TZ3 - Trip zone 3 (I)                           |

| 1-0  | GPIO16 |       | Configure the GPIO16 pin as:                    |

|      |        | 00    | GPIO16 - General purpose I/O 16 (default) (I/O) |

|      |        | 01    | SPISIMOA - SPI-A slave-in, master-out (I/O),    |

|      |        | 10    | Reserved                                        |

|      |        | 11    | TZ2 - Trip zone 2 (I)                           |

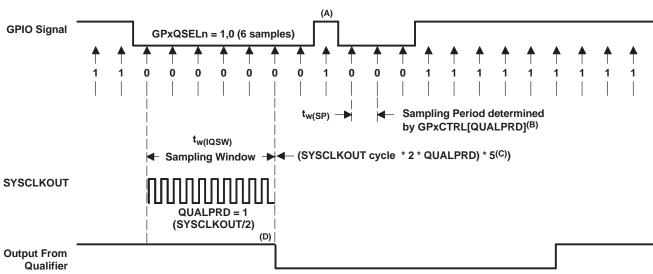

## Figure 53. GPIO Port B MUX 1 (GPBMUX1) Register

| 31       | 16          |     |     |        |     |        |       |        |   |        |   |        |     |     |

|----------|-------------|-----|-----|--------|-----|--------|-------|--------|---|--------|---|--------|-----|-----|

|          |             |     |     |        |     | Res    | erved |        |   |        |   |        |     |     |

|          |             | R-0 |     |        |     |        |       |        |   |        |   |        |     |     |

| 15 14    | 13          | 12  | 11  | 10     | 9   | 8      | 7     | 6      | 5 | 4      | 3 | 2      | 1   | 0   |

| Reserved | GP          | O38 | GPI | GPIO37 |     | GPIO36 |       | GPIO35 |   | GPIO34 |   | GPIO33 |     | O32 |

| R-0      | R/W-0 R/W-0 |     | N-0 | R/V    | V-0 | R/W-0  |       | R/W-0  |   | R/W-0  |   | R/\    | V-0 |     |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 62. GPIO Port B MUX 1 (GPBMUX1) Register Field Descriptions

| Bit   | Field          | Value    | Description                                                                                                                                                                                                         |

|-------|----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-14 | Reserved       |          |                                                                                                                                                                                                                     |

| 13-12 | GPIO38/XCLKIN/ |          | Configure this pin as:                                                                                                                                                                                              |

|       | ТСК            | 00       | GPIO 38 - general purpose I/O 38 (default) (I/O). If $\overline{\text{TRST}} = 1$ , JTAG TCK function is chosen for this pin. This pin can also be used to provide a clock from an external oscillator to the core. |

|       |                | 01       | Reserved                                                                                                                                                                                                            |

|       |                | 10 or 11 | Reserved                                                                                                                                                                                                            |

| 11:10 | GPIO37/TDO     |          | Configure this pin as:                                                                                                                                                                                              |

|       |                | 00       | GPIO 37 - general purpose I/O 37 (default). If TRST = 1, JTAG TDO function is chosen for this pin.                                                                                                                  |

|       |                | 01       | Reserved                                                                                                                                                                                                            |

|       |                | 10 or 11 | Reserved                                                                                                                                                                                                            |

| 9:8   | GPIO36/TMS     |          | Configure this pin as:                                                                                                                                                                                              |

|       |                | 00       | GPIO 36 - general purpose I/O 36 (default). If TRST = 1, JTAG TMS function is chosen for this pin.                                                                                                                  |

|       |                | 01       | Reserved                                                                                                                                                                                                            |

|       |                | 10 or 11 | Reserved                                                                                                                                                                                                            |

| 7:6   | GPIO35/TDI     |          | Configure this pin as:                                                                                                                                                                                              |

|       |                | 00       | GPIO 35 - general purpose I/O 35 (default). If TRST = 1, JTAG TDI function is chosen for this pin.                                                                                                                  |

|       |                | 01       | Reserved                                                                                                                                                                                                            |

|       |                | 10 or 11 | Reserved                                                                                                                                                                                                            |

## Table 62. GPIO Port B MUX 1 (GPBMUX1) Register Field Descriptions (continued)

| Bit | Field  | Value | Description                                                       |

|-----|--------|-------|-------------------------------------------------------------------|

| 5:4 | GPIO34 |       | Configure this pin as:                                            |

|     |        | 00    | GPIO 34 - general purpose I/O 34 (default)                        |

|     |        | 01    | COMP2OUT (O)                                                      |

|     |        | 10    | Reserved                                                          |

|     |        | 11    | Reserved                                                          |

| 3:2 | GPIO33 |       | Configure this pin as:                                            |

|     |        | 00    | GPIO 33 - general purpose I/O 33 (default)                        |

|     |        | 01    | SCLA - I <sup>2</sup> C clock open drain bidirectional port (I/O) |

|     |        | 10    | EPWMSYNCO - External ePWM sync pulse output (O)                   |

|     |        | 11    | ADCSOCBO - ADC start-of-conversion B (O)                          |

| 1:0 | GPIO32 |       | Configure this pin as:                                            |

|     |        | 00    | GPIO 32 - general purpose I/O 32 (default)                        |

|     |        | 01    | SDAA - I <sup>2</sup> C data open drain bidirectional port (I/O)  |

|     |        | 10    | EPWMSYNCI - External ePWM sync pulse input (I)                    |

|     |        | 11    | ADCSOCAO - ADC start-of-conversion A (O)                          |

## Figure 54. Analog I/O MUX (AIOMUX1) Register

| 31   | 30    | 29  | 28    | 27   | 26    | 25  | 24    | 23   | 22    | 21      | 20         | 19       |          | 16 |

|------|-------|-----|-------|------|-------|-----|-------|------|-------|---------|------------|----------|----------|----|

| Rese | erved | AIC | 014   | Rese | erved | AIC | 012   | Rese | erved | AIC     | D10        | Reserved |          |    |

| R    | -0    | R/W | /-1,x | R    | -0    | R/W | /-1,x | R    | -0    | R/W     | R/W-1,x    |          | R-0      |    |

| 15   | 14    | 13  | 12    | 11   | 10    | 9   | 8     | 7    | 6     | 5       | 4          | 3        |          | 0  |

| Rese | erved | Al  | D6    | Rese | erved | Al  | 04    | Rese | erved | Al      | <b>D</b> 2 |          | Reserved |    |

| R    | -0    | R/W | /-1,x | R    | -0    | R/W | /-1,x | R    | -0    | R/W-1,x |            | R-0      |          |    |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 63. Analog I/O MUX (AIOMUX1) Register Field Descriptions

| Bit   | Field    | Value    | Description                                               |

|-------|----------|----------|-----------------------------------------------------------|

| 31:30 | Reserved |          | Any writes to these bit(s) must always have a value of 0. |

| 29:28 | AIO14    | 00 or 01 | AIO14 enabled                                             |

|       |          | 10 or 11 | AIO14 disabled (default)                                  |

| 27:26 | Reserved |          | Any writes to these bit(s) must always have a value of 0. |

| 25:24 | AIO12    | 00 or 01 | AIO12 enabled                                             |

|       |          | 10 or 11 | AIO12 disabled (default)                                  |

| 23:22 | Reserved |          | Any writes to these bit(s) must always have a value of 0. |

| 21:20 | AIO10    | 00 or 01 | AIO10 enabled                                             |

|       |          | 10 or 11 | AIO10 disabled (default)                                  |

| 19:14 | Reserved |          | Any writes to these bit(s) must always have a value of 0. |

| 13:12 | AIO6     | 00 or 01 | AIO6 enabled                                              |

|       |          | 10 or 11 | AIO6 disabled (default)                                   |

| 11:10 | Reserved |          | Any writes to these bit(s) must always have a value of 0. |

| 9:8   | AIO4     | 00 or 01 | AIO4 enabled                                              |

|       |          | 10 or 11 | AIO4 disabled (default)                                   |

| 7:6   | Reserved |          | Any writes to these bit(s) must always have a value of 0. |

| 5:4   | AIO2     | 00 or 01 | AIO2 enabled                                              |

|       |          | 10 or 11 | AIO2 disabled (default)                                   |

### Table 63. Analog I/O MUX (AIOMUX1) Register Field Descriptions (continued)

| Bit | Field    | Value | Description                                               |

|-----|----------|-------|-----------------------------------------------------------|

| 3:0 | Reserved |       | Any writes to these bit(s) must always have a value of 0. |

## Figure 55. GPIO Port A Qualification Control (GPACTRL) Register

| 31 |          | 24 | 23 |          | 16 |

|----|----------|----|----|----------|----|

|    | QUALPRD3 |    |    | QUALPRD2 |    |

|    | R/W-0    |    |    | R/W-0    |    |

| 15 |          | 8  | 7  |          | 0  |

|    | QUALPRD1 |    |    | QUALPRD0 |    |

|    | R/W-0    |    |    | R/W-0    |    |

LEGEND: R/W = Read/Write; R = Read only; -*n* = value after reset

The GPxCTRL registers specify the sampling period for input pins when configured for input qualification using a window of 3 or 6 samples. The sampling period is the amount of time between qualification samples relative to the period of SYSCLKOUT. The number of samples is specified in the GPxQSELn registers.

## Table 64. GPIO Port A Qualification Control (GPACTRL) Register Field Descriptions

| Bits  | Field    | Value | Description (1)                                          |

|-------|----------|-------|----------------------------------------------------------|

| 31-24 | QUALPRD3 |       | Specifies the sampling period for pins GPIO24 to GPIO31. |

|       |          | 0x00  | Sampling Period = $T_{SYSCLKOUT}$ <sup>(2)</sup>         |

|       |          | 0x01  | Sampling Period = 2 × T <sub>SYSCLKOUT</sub>             |

|       |          | 0x02  | Sampling Period = 4 × T <sub>SYSCLKOUT</sub>             |

|       |          |       |                                                          |

|       |          | 0xFF  | Sampling Period = 510 × T <sub>SYSCLKOUT</sub>           |

| 23-16 | QUALPRD2 |       | Specifies the sampling period for pins GPIO16 to GPIO23. |

|       |          | 0x00  | Sampling Period = $T_{SYSCLKOUT}$ <sup>(2)</sup>         |

|       |          | 0x01  | Sampling Period = 2 × T <sub>SYSCLKOUT</sub>             |

|       |          | 0x02  | Sampling Period = 4 × T <sub>SYSCLKOUT</sub>             |

|       |          |       |                                                          |

|       |          | 0xFF  | Sampling Period = 510 × T <sub>SYSCLKOUT</sub>           |

| 15-8  | QUALPRD1 |       | Specifies the sampling period for pins GPIO8 to GPIO15.  |

|       |          | 0x00  | Sampling Period = $T_{SYSCLKOUT}$ <sup>(2)</sup>         |

|       |          | 0x01  | Sampling Period = 2 × T <sub>SYSCLKOUT</sub>             |

|       |          | 0x02  | Sampling Period = 4 × T <sub>SYSCLKOUT</sub>             |

|       |          |       |                                                          |

|       |          | 0xFF  | Sampling Period = 510 × T <sub>SYSCLKOUT</sub>           |

| 7-0   | QUALPRD0 |       | Specifies the sampling period for pins GPIO0 to GPIO7.   |

|       |          | 0x00  | Sampling Period = $T_{SYSCLKOUT}$ <sup>(2)</sup>         |

|       |          | 0x01  | Sampling Period = 2 × T <sub>SYSCLKOUT</sub>             |

|       |          | 0x02  | Sampling Period = 4 × T <sub>SYSCLKOUT</sub>             |

|       |          |       |                                                          |

|       |          | 0xFF  | Sampling Period = 510 × T <sub>SYSCLKOUT</sub>           |

<sup>(1)</sup> This register is EALLOW protected. See Section 5.2 for more information.

$^{(2)}$   $T_{\text{SYSCLKOUT}}$  indicates the period of SYSCLKOUT.

General-Purpose Input/Output (GPIO)

# Figure 56. GPIO Port B Qualification Control (GPBCTRL) Register

| 31 |          |      |          |       | 16 |  |  |

|----|----------|------|----------|-------|----|--|--|

|    |          | Rese | erved    |       |    |  |  |

|    | R-0      |      |          |       |    |  |  |

| 15 |          | 8    | 7        |       | 0  |  |  |

|    | Reserved |      | QUALPRD0 |       |    |  |  |

|    | R-0      |      |          | R/W-0 |    |  |  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 65. GPIO Port B Qualification Control (GPBCTRL) Register Field Descriptions

| Bits  | Field    | Value | Description <sup>(1)</sup>                              |

|-------|----------|-------|---------------------------------------------------------|

| 31- 8 | Reserved |       | Reserved                                                |

| 7-0   | QUALPRD0 |       | Specifies the sampling period for pins GPIO32 to GPIO38 |

|       |          | 0xFF  | Sampling Period = 510 × T <sub>SYSCLKOUT</sub>          |

|       |          | 0x00  | Sampling Period = $T_{SYSCLKOUT}$ <sup>(2)</sup>        |

|       |          | 0x01  | Sampling Period = $2 \times T_{SYSCLKOUT}$              |

|       |          | 0x02  | Sampling Period = 4 × T <sub>SYSCLKOUT</sub>            |

|       |          |       |                                                         |

|       |          | 0xFF  | Sampling Period = 510 × T <sub>SYSCLKOUT</sub>          |

<sup>(1)</sup> This register is EALLOW protected. See Section 5.2 for more information.

$^{(2)}$  T<sub>SYSCLKOUT</sub> indicates the period of SYSCLKOUT.

### General-Purpose Input/Output (GPIO)

Figure 57. GPIO Port A Qualification Select 1 (GPAQSEL1) Register 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 GPIO15 GPIO14 GPIO13 GPIO12 GPIO11 GPIO10 GPIO9 GPIO8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 15 6 5 2 1 14 13 12 11 10 9 8 7 4 3 0 GPIO7 GPIO6 GPIO5 GPIO4 GPIO3 GPIO2 GPIO1 GPIO0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -*n* = value after reset

### Table 66. GPIO Port A Qualification Select 1 (GPAQSEL1) Register Field Descriptions

| Bits | Field             | Value | Description <sup>(1)</sup>                                                                                                                                                                                                  |

|------|-------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-0 | 31-0 GPIO15-GPIO0 |       | Select input qualification type for GPIO0 to GPIO15. The input qualification of each GPIO input is controlled by two bits as shown in Figure 57.                                                                            |

|      |                   | 00    | Synchronize to SYSCLKOUT only. Valid for both peripheral and GPIO pins.                                                                                                                                                     |

|      |                   | 01    | Qualification using 3 samples. Valid for pins configured as GPIO or a peripheral function. The time between samples is specified in the GPACTRL register.                                                                   |

|      |                   | 10    | Qualification using 6 samples. Valid for pins configured as GPIO or a peripheral function. The time between samples is specified in the GPACTRL register.                                                                   |

|      |                   | 11    | Asynchronous. (no synchronization or qualification). This option applies to pins configured as peripherals only. If the pin is configured as a GPIO input, then this option is the same as 0,0 or synchronize to SYSCLKOUT. |

<sup>(1)</sup> This register is EALLOW protected. See Section 5.2 for more information.

### Figure 58. GPIO Port A Qualification Select 2 (GPAQSEL2) Register

| 31 30  | 29 28         | 27 26  | 25 24  | 23 22  | 21 20  | 19 18  | 17 16  |

|--------|---------------|--------|--------|--------|--------|--------|--------|

| GPIO31 | GPIO30        | GPIO29 | GPIO28 | GPIO27 | GPIO26 | GPIO25 | GPIO24 |

| R/W-0  | R/W-0         | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

| 15 14  | 13 12         | 11 10  | 9 8    | 7 6    | 5 4    | 3 2    | 1 0    |

| GPIO23 | GPIO23 GPIO22 |        | GPIO20 | GPIO19 | GPIO18 | GPIO17 | GPIO16 |

| R/W-0  | R/W-0         | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 67. GPIO Port A Qualification Select 2 (GPAQSEL2) Register Field Descriptions

| Bits | Field              | Value | Description <sup>(1)</sup>                                                                                                                                                                                                  |

|------|--------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-0 | 31-0 GPIO31-GPIO16 |       | Select input qualification type for GPIO16 to GPIO31. The input qualification of each GPIO input is controlled by two bits as shown in Figure 58.                                                                           |

|      |                    | 00    | Synchronize to SYSCLKOUT only. Valid for both peripheral and GPIO pins.                                                                                                                                                     |

|      |                    | 01    | Qualification using 3 samples. Valid for pins configured as GPIO or a peripheral function. The time between samples is specified in the GPACTRL register.                                                                   |

|      |                    | 10    | Qualification using 6 samples. Valid for pins configured as GPIO or a peripheral function. The time between samples is specified in the GPACTRL register.                                                                   |

|      |                    | 11    | Asynchronous. (no synchronization or qualification). This option applies to pins configured as peripherals only. If the pin is configured as a GPIO input, then this option is the same as 0,0 or synchronize to SYSCLKOUT. |

<sup>(1)</sup> This register is EALLOW protected. See Section 5.2 for more information.

General-Purpose Input/Output (GPIO)

www.ti.com

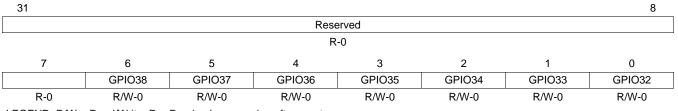

# Figure 59. GPIO Port B Qualification Select 1 (GPBQSEL1) Register

| 31   |             |     |     |     |     |     |     |       |     |     |     |     |     |     | 16  |

|------|-------------|-----|-----|-----|-----|-----|-----|-------|-----|-----|-----|-----|-----|-----|-----|

|      |             |     |     |     |     |     | Res | erved |     |     |     |     |     |     |     |

|      |             |     |     |     |     |     | F   | 8-0   |     |     |     |     |     |     |     |

| 15   | 14          | 13  | 12  | 11  | 10  | 9   | 8   | 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Rese | erved       | GPI | O38 | GPI | O37 | GPI | O36 | GPI   | O35 | GPI | O34 | GP  | O33 | GPI | O32 |

| R/V  | R/W-0 R/W-0 |     | RΛ  | V-0 | R/\ | V-0 | R/\ | V-0   | R/\ | V-0 | R/  | N-0 | R/\ | N-0 |     |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

### Table 68. GPIO Port B Qualification Select 1 (GPBQSEL1) Register Field Descriptions

| Bits   | Field          | Value | Description <sup>(1)</sup>                                                                                                                                                                                                  |

|--------|----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31- 14 | Reserved       |       |                                                                                                                                                                                                                             |

| 13 -0  | GPIO38 -GPIO32 |       | Select input qualification type for GPIO32 to GPIO38 . The input qualification of each GPIO input is controlled by two bits as shown in Figure 59.                                                                          |

|        |                | 00    | Synchronize to SYSCLKOUT only. Valid for both peripheral and GPIO pins.                                                                                                                                                     |

|        |                | 01    | Qualification using 3 samples. Valid for pins configured as GPIO or a peripheral function. The time between samples is specified in the GPACTRL register.                                                                   |

|        |                | 10    | Qualification using 6 samples. Valid for pins configured as GPIO or a peripheral function.<br>The time between samples is specified in the GPACTRL register.                                                                |

|        |                | 11    | Asynchronous. (no synchronization or qualification). This option applies to pins configured as peripherals only. If the pin is configured as a GPIO input, then this option is the same as 0,0 or synchronize to SYSCLKOUT. |